#include "xil_printf.h"#include "debug.h"#include "io_access.h"#include "nvme.h"#include "host_lld.h"#include "nvme_main.h"#include "nvme_admin_cmd.h"#include "nvme_io_cmd.h"#include "../memory_map.h"

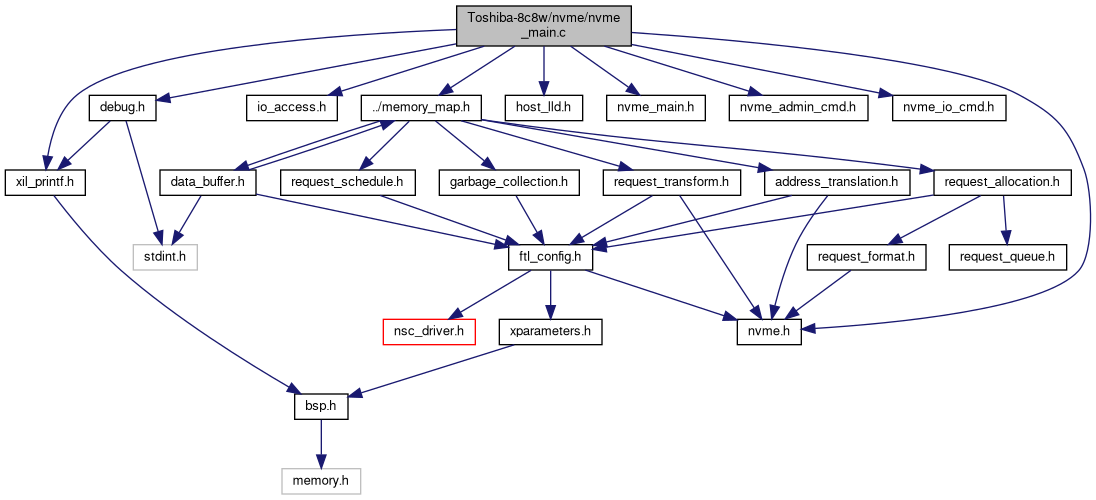

Include dependency graph for nvme_main.c:

Go to the source code of this file.

Functions | |

| void | nvme_main () |

Variables | |

| volatile NVME_CONTEXT | g_nvmeTask |

Function Documentation

◆ nvme_main()

| void nvme_main | ( | ) |

The main loop of Cosmos+ firmware.

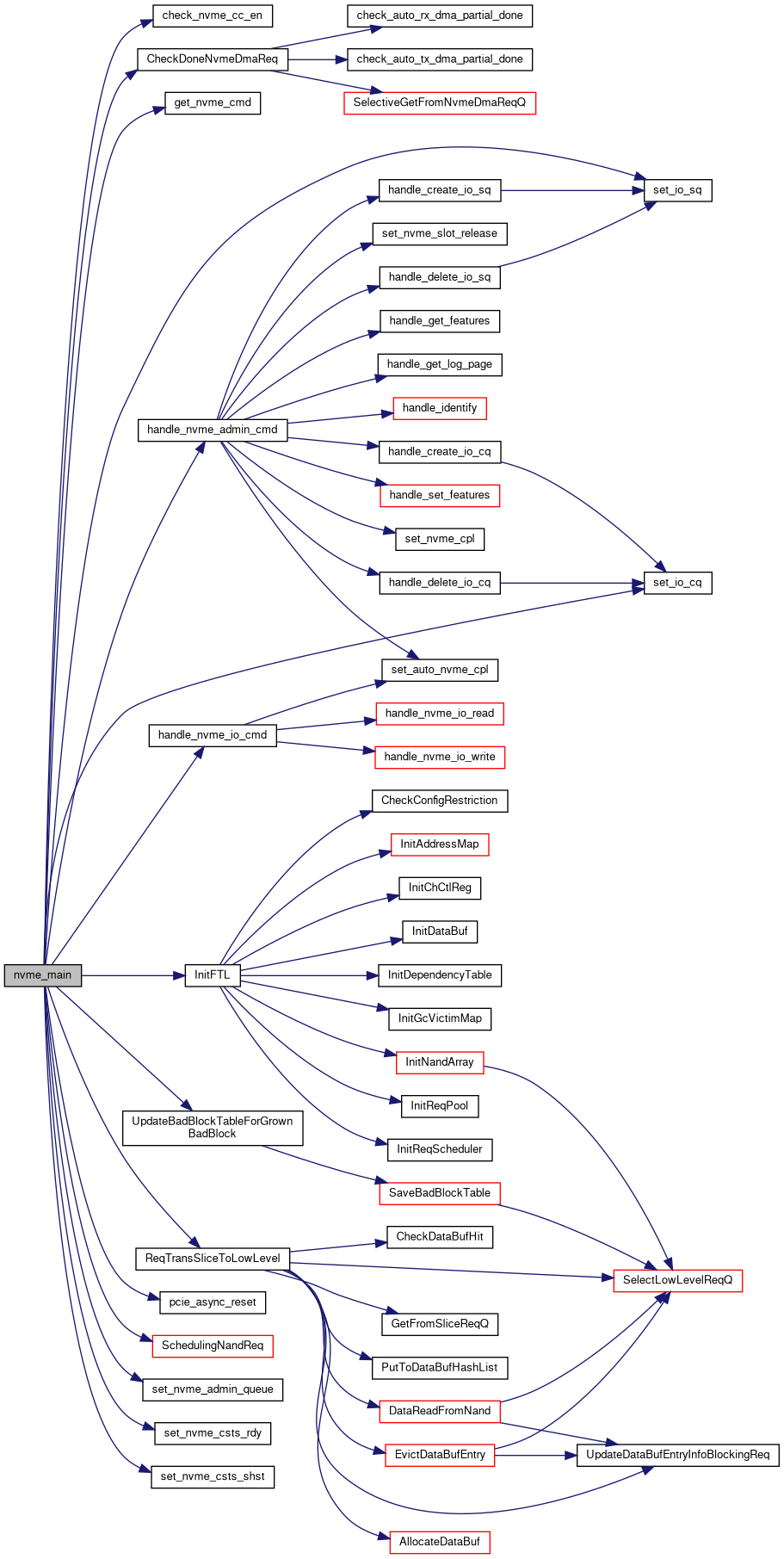

This loop can be separated into several small parts:

- NVMe Manager

Low-level Scheduler

Interpret NVMe commands received from host.

In this step, we need to check which type of the NVMe command you got:

- If it's Admin command:

Handle it in NVMe Manager without forwarding to FTL.

- If it's I/O (NVM) command:

Forward to the NVM Command Manager (FTL).

Do scheduling.

We need to execute the requests that were put on corresponding queue in prev part.

As described in the paper, Host DMA operations have the highest priority, so we should call the CheckDoneNvmeDmaReq first, then SchedulingNandReq.

Definition at line 73 of file nvme_main.c.

74{

75 unsigned int exeLlr;

76 unsigned int rstCnt = 0;

77

78 xil_printf("!!! Wait until FTL reset complete !!! \r\n");

79

80 InitFTL();

81

82 xil_printf("\r\nFTL reset complete!!! \r\n");

83 xil_printf("Turn on the host PC \r\n");

84

93 while (1)

94 {

95 exeLlr = 1;

96

98 {

99 unsigned int ccEn;

100 ccEn = check_nvme_cc_en();

101 if (ccEn == 1)

102 {

103 set_nvme_admin_queue(1, 1, 1);

104 set_nvme_csts_rdy(1);

106 xil_printf("\r\nNVMe ready!!!\r\n");

107 }

108 }

110 {

111 NVME_COMMAND nvmeCmd;

112 unsigned int cmdValid;

113

114 cmdValid = get_nvme_cmd(&nvmeCmd.qID, &nvmeCmd.cmdSlotTag, &nvmeCmd.cmdSeqNum, nvmeCmd.cmdDword);

115

129 if (cmdValid == 1)

130 {

131 rstCnt = 0;

133 {

134 handle_nvme_admin_cmd(&nvmeCmd);

135 }

136 else

137 {

138 handle_nvme_io_cmd(&nvmeCmd);

139 ReqTransSliceToLowLevel();

140 exeLlr = 0;

141 }

142 }

143 }

145 {

146 NVME_STATUS_REG nvmeReg;

149 {

150 unsigned int qID;

151 set_nvme_csts_shst(1);

152

153 for (qID = 0; qID < 8; qID++)

154 {

155 set_io_cq(qID, 0, 0, 0, 0, 0, 0);

156 set_io_sq(qID, 0, 0, 0, 0, 0);

157 }

158

159 set_nvme_admin_queue(0, 0, 0);

161 set_nvme_csts_shst(2);

163

164 // flush grown bad block info

166

167 xil_printf("\r\nNVMe shutdown!!!\r\n");

168 }

169 }

171 {

172 unsigned int ccEn;

173 ccEn = check_nvme_cc_en();

174 if (ccEn == 0)

175 {

177 set_nvme_csts_shst(0);

178 set_nvme_csts_rdy(0);

180 xil_printf("\r\nNVMe disable!!!\r\n");

181 }

182 }

184 {

185 unsigned int qID;

186 for (qID = 0; qID < 8; qID++)

187 {

188 set_io_cq(qID, 0, 0, 0, 0, 0, 0);

189 set_io_sq(qID, 0, 0, 0, 0, 0);

190 }

191

192 if (rstCnt >= 5)

193 {

194 pcie_async_reset(rstCnt);

195 rstCnt = 0;

196 xil_printf("\r\nPcie iink disable!!!\r\n");

197 xil_printf("Wait few minute or reconnect the PCIe cable\r\n");

198 }

199 else

200 rstCnt++;

201

203 set_nvme_admin_queue(0, 0, 0);

204 set_nvme_csts_shst(0);

205 set_nvme_csts_rdy(0);

207

208 xil_printf("\r\nNVMe reset!!!\r\n");

209 }

210

220 if (exeLlr && ((nvmeDmaReqQ.headReq != REQ_SLOT_TAG_NONE) || notCompletedNandReqCnt || blockedReqCnt))

221 {

222 CheckDoneNvmeDmaReq();

223 SchedulingNandReq();

224 }

225 }

226}

void UpdateBadBlockTableForGrownBadBlock(unsigned int tempBufAddr)

Update the bad block table and persist to the specified block.

Definition: address_translation.c:1254

void set_nvme_admin_queue(unsigned int sqValid, unsigned int cqValid, unsigned int cqIrqEn)

Definition: host_lld.c:225

unsigned int get_nvme_cmd(unsigned short *qID, unsigned short *cmdSlotTag, unsigned int *cmdSeqNum, unsigned int *cmdDword)

Definition: host_lld.c:237

void set_io_sq(unsigned int ioSqIdx, unsigned int valid, unsigned int cqVector, unsigned int qSzie, unsigned int pcieBaseAddrL, unsigned int pcieBaseAddrH)

Definition: host_lld.c:301

void set_io_cq(unsigned int ioCqIdx, unsigned int valid, unsigned int irqEn, unsigned int irqVector, unsigned int qSzie, unsigned int pcieBaseAddrL, unsigned int pcieBaseAddrH)

Definition: host_lld.c:318

void handle_nvme_admin_cmd(NVME_COMMAND *nvmeCmd)

Definition: nvme_admin_cmd.c:415

void SchedulingNandReq()

Iteratively do schedule on each channel by calling SchedulingNandReqPerCh.

Definition: request_schedule.c:186

void ReqTransSliceToLowLevel()

Data Buffer Manager. Handle all the pending slice requests.

Definition: request_transform.c:323

Definition: nvme.h:206

Definition: host_lld.h:149

Here is the call graph for this function:

Here is the caller graph for this function:

Variable Documentation

◆ g_nvmeTask

| volatile NVME_CONTEXT g_nvmeTask |

Definition at line 71 of file nvme_main.c.