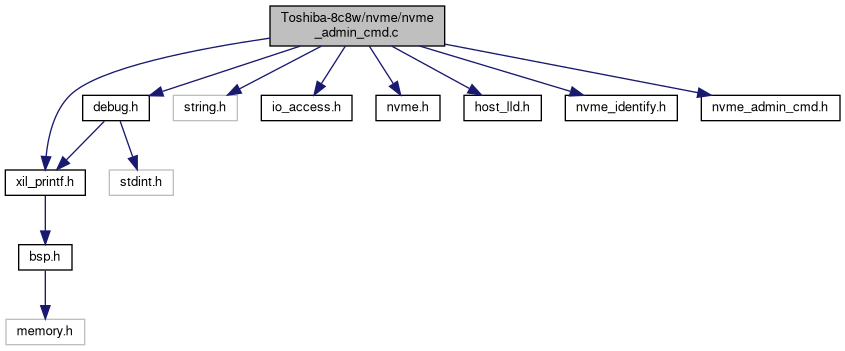

#include "xil_printf.h"#include "debug.h"#include "string.h"#include "io_access.h"#include "nvme.h"#include "host_lld.h"#include "nvme_identify.h"#include "nvme_admin_cmd.h"

Include dependency graph for nvme_admin_cmd.c:

Go to the source code of this file.

Functions | |

| unsigned int | get_num_of_queue (unsigned int dword11) |

| void | handle_set_features (NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL) |

| void | handle_get_features (NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL) |

| void | handle_create_io_sq (NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL) |

| void | handle_delete_io_sq (NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL) |

| void | handle_create_io_cq (NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL) |

| void | handle_delete_io_cq (NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL) |

| void | handle_identify (NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL) |

| void | handle_get_log_page (NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL) |

| void | handle_nvme_admin_cmd (NVME_COMMAND *nvmeCmd) |

Variables | |

| NVME_CONTEXT | g_nvmeTask |

Function Documentation

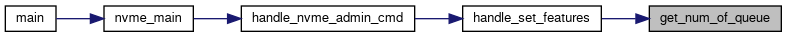

◆ get_num_of_queue()

| unsigned int get_num_of_queue | ( | unsigned int | dword11 | ) |

Definition at line 59 of file nvme_admin_cmd.c.

60{

61 ADMIN_SET_FEATURES_NUMBER_OF_QUEUES_DW11 requested;

62 ADMIN_SET_FEATURES_NUMBER_OF_QUEUES_COMPLETE allocated;

63

64 requested.dword = dword11;

65 xil_printf("Number of IO Submission Queues Requested (NSQR, zero-based): 0x%04X\r\n", requested.NSQR);

66 xil_printf("Number of IO Completion Queues Requested (NCQR, zero-based): 0x%04X\r\n", requested.NCQR);

67

68 // IO submission queue allocating

71 else

72 g_nvmeTask.numOfIOSubmissionQueuesAllocated = requested.NSQR + 1; // zero-based -> non zero-based

73

74 allocated.NSQA = g_nvmeTask.numOfIOSubmissionQueuesAllocated - 1; // non zero-based -> zero-based

75

76 // IO completion queue allocating

79 else

80 g_nvmeTask.numOfIOCompletionQueuesAllocated = requested.NCQR + 1; // zero-based -> non zero-based

81

82 allocated.NCQA = g_nvmeTask.numOfIOCompletionQueuesAllocated - 1; // non zero-based -> zero-based

83

84 xil_printf("Number of IO Submission Queues Allocated (NSQA, zero-based): 0x%04X\r\n", allocated.NSQA);

85 xil_printf("Number of IO Completion Queues Allocated (NCQA, zero-based): 0x%04X\r\n", allocated.NCQA);

86

88}

unsigned short numOfIOSubmissionQueuesAllocated

Definition: nvme.h:962

unsigned short numOfIOCompletionQueuesAllocated

Definition: nvme.h:963

Here is the caller graph for this function:

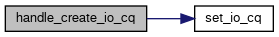

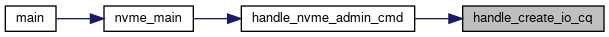

◆ handle_create_io_cq()

| void handle_create_io_cq | ( | NVME_ADMIN_COMMAND * | nvmeAdminCmd, |

| NVME_COMPLETION * | nvmeCPL | ||

| ) |

Definition at line 274 of file nvme_admin_cmd.c.

275{

276 ADMIN_CREATE_IO_CQ_DW10 cqInfo10;

277 ADMIN_CREATE_IO_CQ_DW11 cqInfo11;

278 NVME_IO_CQ_STATUS *ioCqStatus;

279 unsigned int ioCqIdx;

280

283

285

288

289 ioCqIdx = cqInfo10.QID - 1;

291

292 ioCqStatus->valid = 1;

298

299 set_io_cq(ioCqIdx, ioCqStatus->valid, ioCqStatus->irqEn, ioCqStatus->irqVector, ioCqStatus->qSzie,

301

302 nvmeCPL->dword[0] = 0;

303 nvmeCPL->specific = 0x0;

304}

void set_io_cq(unsigned int ioCqIdx, unsigned int valid, unsigned int irqEn, unsigned int irqVector, unsigned int qSzie, unsigned int pcieBaseAddrL, unsigned int pcieBaseAddrH)

Definition: host_lld.c:318

Definition: nvme.h:421

Definition: nvme.h:434

Definition: nvme.h:947

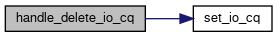

Here is the call graph for this function:

Here is the caller graph for this function:

◆ handle_create_io_sq()

| void handle_create_io_sq | ( | NVME_ADMIN_COMMAND * | nvmeAdminCmd, |

| NVME_COMPLETION * | nvmeCPL | ||

| ) |

Definition at line 213 of file nvme_admin_cmd.c.

214{

215 ADMIN_CREATE_IO_SQ_DW10 sqInfo10;

216 ADMIN_CREATE_IO_SQ_DW11 sqInfo11;

217 NVME_IO_SQ_STATUS *ioSqStatus;

218 unsigned int ioSqIdx;

219

222

224 /*xil_printf("QID : 0x%08X, QSIZE : 0x%08X\r\n", sqInfo10.QID, sqInfo10.QSIZE);

225 xil_printf("PC : 0x%08X, QPRIO : 0x%08X, CQID : 0x%08X\r\n", sqInfo11.PC, sqInfo11.QPRIO,sqInfo11.CQID);

226 xil_printf("pcieBaseAddrL : 0x%08X, pcieBaseAddrH : 0x%08X\r\n", ioSqStatus->pcieBaseAddrL,

227 ioSqStatus->pcieBaseAddrH);*/

228

231 sqInfo11.CQID <= 8);

232

233 ioSqIdx = sqInfo10.QID - 1;

235

236 ioSqStatus->valid = 1;

241

242 set_io_sq(ioSqIdx, ioSqStatus->valid, ioSqStatus->cqVector, ioSqStatus->qSzie, ioSqStatus->pcieBaseAddrL,

243 ioSqStatus->pcieBaseAddrH);

244

245 nvmeCPL->dword[0] = 0;

246 nvmeCPL->specific = 0x0;

247}

void set_io_sq(unsigned int ioSqIdx, unsigned int valid, unsigned int cqVector, unsigned int qSzie, unsigned int pcieBaseAddrL, unsigned int pcieBaseAddrH)

Definition: host_lld.c:301

Definition: nvme.h:464

Definition: nvme.h:477

Definition: nvme.h:938

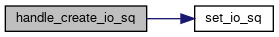

Here is the call graph for this function:

Here is the caller graph for this function:

◆ handle_delete_io_cq()

| void handle_delete_io_cq | ( | NVME_ADMIN_COMMAND * | nvmeAdminCmd, |

| NVME_COMPLETION * | nvmeCPL | ||

| ) |

Definition at line 306 of file nvme_admin_cmd.c.

307{

308 ADMIN_DELETE_IO_CQ_DW10 cqInfo10;

309 NVME_IO_CQ_STATUS *ioCqStatus;

310 unsigned int ioCqIdx;

311

313

315

318

319 ioCqStatus->valid = 0;

320 ioCqStatus->irqVector = 0;

321 ioCqStatus->qSzie = 0;

322 ioCqStatus->pcieBaseAddrL = 0;

323 ioCqStatus->pcieBaseAddrH = 0;

324

325 set_io_cq(ioCqIdx, 0, 0, 0, 0, 0, 0);

326

327 nvmeCPL->dword[0] = 0;

328 nvmeCPL->specific = 0x0;

329}

Definition: nvme.h:450

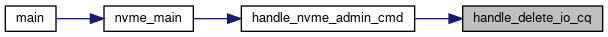

Here is the call graph for this function:

Here is the caller graph for this function:

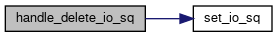

◆ handle_delete_io_sq()

| void handle_delete_io_sq | ( | NVME_ADMIN_COMMAND * | nvmeAdminCmd, |

| NVME_COMPLETION * | nvmeCPL | ||

| ) |

Definition at line 249 of file nvme_admin_cmd.c.

250{

251 ADMIN_DELETE_IO_SQ_DW10 sqInfo10;

252 NVME_IO_SQ_STATUS *ioSqStatus;

253 unsigned int ioSqIdx;

254

256

258

261

262 ioSqStatus->valid = 0;

263 ioSqStatus->cqVector = 0;

264 ioSqStatus->qSzie = 0;

265 ioSqStatus->pcieBaseAddrL = 0;

266 ioSqStatus->pcieBaseAddrH = 0;

267

268 set_io_sq(ioSqIdx, 0, 0, 0, 0, 0);

269

270 nvmeCPL->dword[0] = 0;

271 nvmeCPL->specific = 0x0;

272}

Definition: nvme.h:493

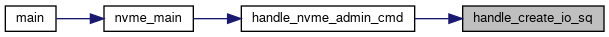

Here is the call graph for this function:

Here is the caller graph for this function:

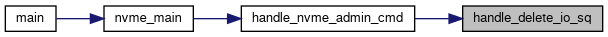

◆ handle_get_features()

| void handle_get_features | ( | NVME_ADMIN_COMMAND * | nvmeAdminCmd, |

| NVME_COMPLETION * | nvmeCPL | ||

| ) |

Definition at line 152 of file nvme_admin_cmd.c.

153{

154 ADMIN_GET_FEATURES_DW10 features;

155 NVME_COMPLETION cpl;

156

158

160 {

162 {

164

165 cpl.dword[0] = 0x0;

168 nvmeCPL->specific = 0x0;

169 break;

170 }

172 {

173 nvmeCPL->dword[0] = 0x0;

175 break;

176 }

178 {

179

181 nvmeCPL->dword[0] = 0x0;

183 break;

184 }

186 {

187 nvmeCPL->dword[0] = 0x0;

188 nvmeCPL->specific = 0x0;

189 break;

190 }

192 {

193 nvmeCPL->dword[0] = 0x0;

194 nvmeCPL->specific = 0x0;

195 break;

196 }

197 case 0xD0:

198 {

199 nvmeCPL->dword[0] = 0x0;

200 nvmeCPL->specific = 0x0;

201 break;

202 }

203 default:

204 {

206 ASSERT(0);

207 break;

208 }

209 }

211}

Definition: nvme.h:405

struct _NVME_COMPLETION::@72::@74::@76::@78 statusField

Here is the caller graph for this function:

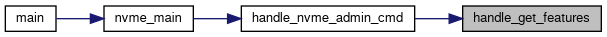

◆ handle_get_log_page()

| void handle_get_log_page | ( | NVME_ADMIN_COMMAND * | nvmeAdminCmd, |

| NVME_COMPLETION * | nvmeCPL | ||

| ) |

Definition at line 384 of file nvme_admin_cmd.c.

385{

386 // ADMIN_GET_LOG_PAGE_DW10 getLogPageInfo;

387

388 // unsigned int prp1[2];

389 // unsigned int prp2[2];

390 // unsigned int prpLen;

391

392 // getLogPageInfo.dword = nvmeAdminCmd->dword10;

393

394 // prp1[0] = nvmeAdminCmd->PRP1[0];

395 // prp1[1] = nvmeAdminCmd->PRP1[1];

396 // prpLen = 0x1000 - (prp1[0] & 0xFFF);

397

398 // prp2[0] = nvmeAdminCmd->PRP2[0];

399 // prp2[1] = nvmeAdminCmd->PRP2[1];

400

401 // xil_printf("ADMIN GET LOG PAGE\n");

402

403 // LID

404 // Mandatory//1-Error information, 2-SMART/Health information, 3-Firmware Slot information

405 // Optional//4-ChangedNamespaceList, 5-Command Effects Log

406 // xil_printf("LID: 0x%X, NUMD: 0x%X \r\n", getLogPageInfo.LID, getLogPageInfo.NUMD);

407

408 // xil_printf("PRP1[63:32] = 0x%X, PRP1[31:0] = 0x%X", prp1[1], prp1[0]);

409 // xil_printf("PRP2[63:32] = 0x%X, PRP2[31:0] = 0x%X", prp2[1], prp2[0]);

410

411 nvmeCPL->dword[0] = 0;

413}

Here is the caller graph for this function:

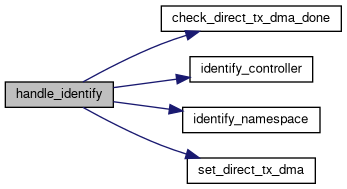

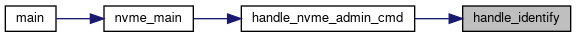

◆ handle_identify()

| void handle_identify | ( | NVME_ADMIN_COMMAND * | nvmeAdminCmd, |

| NVME_COMPLETION * | nvmeCPL | ||

| ) |

Definition at line 331 of file nvme_admin_cmd.c.

332{

333 ADMIN_IDENTIFY_COMMAND_DW10 identifyInfo;

335 unsigned int prp[2];

336 unsigned int prpLen;

337

339

341 {

345

347 identify_controller(pIdentifyData);

348 }

350 {

354 // ASSERT(nvmeAdminCmd->NSID == 1);

356 identify_namespace(pIdentifyData);

357 }

358 else

359 ASSERT(0);

360

361 prp[0] = nvmeAdminCmd->PRP1[0];

362 prp[1] = nvmeAdminCmd->PRP1[1];

363

364 prpLen = 0x1000 - (prp[0] & 0xFFF);

365 // xil_printf("prpLen = %X, prp[1] = %X, prp[0] = %X\r\n",prpLen, prp[1], prp[0]);

366 set_direct_tx_dma(pIdentifyData, prp[1], prp[0], prpLen);

367 if (prpLen != 0x1000)

368 {

369 pIdentifyData = pIdentifyData + prpLen;

370 prpLen = 0x1000 - prpLen;

371 prp[0] = nvmeAdminCmd->PRP2[0];

372 prp[1] = nvmeAdminCmd->PRP2[1];

373

374 // ASSERT((prp[1] & 0xFFF) == 0);

375 // xil_printf("prpLen = %X, prp[1] = %X, prp[0] = %X\r\n",prpLen, prp[1], prp[0]);

376 set_direct_tx_dma(pIdentifyData, prp[1], prp[0], prpLen);

377 }

378

379 check_direct_tx_dma_done();

380 nvmeCPL->dword[0] = 0;

381 nvmeCPL->specific = 0x0;

382}

void set_direct_tx_dma(unsigned int devAddr, unsigned int pcieAddrH, unsigned int pcieAddrL, unsigned int len)

Definition: host_lld.c:336

Definition: nvme.h:507

Here is the call graph for this function:

Here is the caller graph for this function:

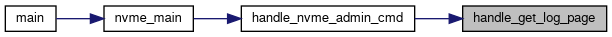

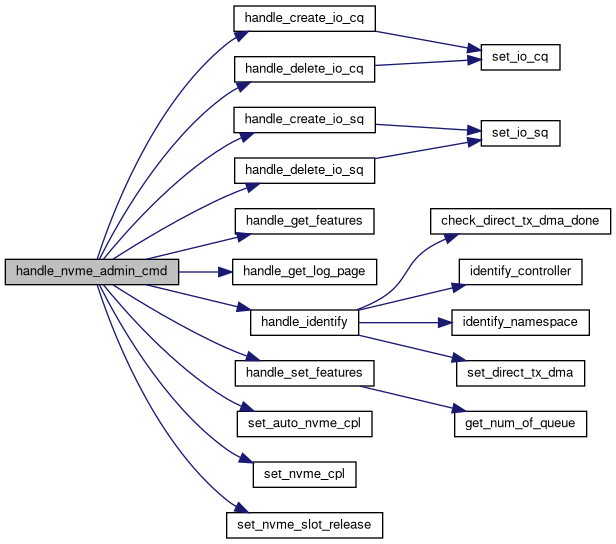

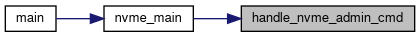

◆ handle_nvme_admin_cmd()

| void handle_nvme_admin_cmd | ( | NVME_COMMAND * | nvmeCmd | ) |

Definition at line 415 of file nvme_admin_cmd.c.

416{

417 NVME_ADMIN_COMMAND *nvmeAdminCmd;

418 NVME_COMPLETION nvmeCPL;

419 unsigned int opc;

420 unsigned int needCpl;

421 unsigned int needSlotRelease;

422

425

426 needCpl = 1;

427 needSlotRelease = 0;

428

429 /* xil_printf("OPC = 0x%X\r\n", nvmeAdminCmd->OPC);

430 xil_printf("FUSE = 0x%X\r\n", nvmeAdminCmd->FUSE);

431 xil_printf("PSDT = 0x%X\r\n", nvmeAdminCmd->PSDT);

432 xil_printf("CID = 0x%X\r\n",nvmeAdminCmd->CID);

433 xil_printf("NSID = 0x%X\r\n", nvmeAdminCmd->NSID);

434 xil_printf("MPTR[1] = 0x%X, MPTR[0] = 0x%X\r\n", nvmeAdminCmd->MPTR[1], nvmeAdminCmd->MPTR[0]);

435 xil_printf("PRP1[63:32] = 0x%X, PRP1[31:0] = 0x%X\r\n", nvmeAdminCmd->PRP1[1],

436 nvmeAdminCmd->PRP1[0]); xil_printf("PRP2[63:32] = 0x%X, PRP2[31:0] = 0x%X\r\n", nvmeAdminCmd->PRP2[1],

437 nvmeAdminCmd->PRP2[0]); xil_printf("dword10 = 0x%X\r\n", nvmeAdminCmd->dword10); xil_printf("dword11 =

438 0x%X\r\n", nvmeAdminCmd->dword11); xil_printf("dword12 = 0x%X\r\n", nvmeAdminCmd->dword12);

439 xil_printf("dword13 = 0x%X\r\n", nvmeAdminCmd->dword13);

440 xil_printf("dword14 = 0x%X\r\n", nvmeAdminCmd->dword14);

441 xil_printf("dword15 = 0x%X\r\n", nvmeAdminCmd->dword15);*/

442 switch (opc)

443 {

445 {

446 handle_set_features(nvmeAdminCmd, &nvmeCPL);

447 break;

448 }

450 {

451 handle_create_io_cq(nvmeAdminCmd, &nvmeCPL);

452 break;

453 }

455 {

456 handle_create_io_sq(nvmeAdminCmd, &nvmeCPL);

457 break;

458 }

460 {

461 handle_identify(nvmeAdminCmd, &nvmeCPL);

462 break;

463 }

465 {

466 handle_get_features(nvmeAdminCmd, &nvmeCPL);

467 break;

468 }

470 {

471 handle_delete_io_cq(nvmeAdminCmd, &nvmeCPL);

472 break;

473 }

475 {

476 handle_delete_io_sq(nvmeAdminCmd, &nvmeCPL);

477 break;

478 }

480 {

481 needCpl = 0;

482 needSlotRelease = 1;

483 nvmeCPL.dword[0] = 0;

484 nvmeCPL.specific = 0x0;

485 break;

486 }

488 {

489 handle_get_log_page(nvmeAdminCmd, &nvmeCPL);

490 break;

491 }

493 {

494 needCpl = 0;

495 needSlotRelease = 0;

496 nvmeCPL.dword[0] = 0;

497 nvmeCPL.specific = 0x0;

498 break;

499 }

501 {

502 needCpl = 0;

503 needSlotRelease = 0;

504 nvmeCPL.dword[0] = 0;

505 nvmeCPL.specific = 0x0;

506 break;

507 }

508 default:

509 {

510 xil_printf("Not Support Admin Command OPC: %X\r\n", opc);

511 ASSERT(0);

512 break;

513 }

514 }

515

516 if (needCpl == 1)

518 else if (needSlotRelease == 1)

520 else

521

523

524 xil_printf("Done Admin Command OPC: %X\r\n", opc);

525}

void set_auto_nvme_cpl(unsigned int cmdSlotTag, unsigned int specific, unsigned int statusFieldWord)

Definition: host_lld.c:260

void set_nvme_cpl(unsigned int sqId, unsigned int cid, unsigned int specific, unsigned int statusFieldWord)

Definition: host_lld.c:286

void handle_get_features(NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL)

Definition: nvme_admin_cmd.c:152

void handle_identify(NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL)

Definition: nvme_admin_cmd.c:331

void handle_create_io_sq(NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL)

Definition: nvme_admin_cmd.c:213

void handle_delete_io_sq(NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL)

Definition: nvme_admin_cmd.c:249

void handle_delete_io_cq(NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL)

Definition: nvme_admin_cmd.c:306

void handle_create_io_cq(NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL)

Definition: nvme_admin_cmd.c:274

void handle_get_log_page(NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL)

Definition: nvme_admin_cmd.c:384

void handle_set_features(NVME_ADMIN_COMMAND *nvmeAdminCmd, NVME_COMPLETION *nvmeCPL)

Definition: nvme_admin_cmd.c:90

Definition: nvme.h:241

Here is the call graph for this function:

Here is the caller graph for this function:

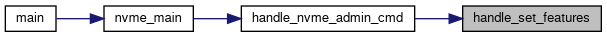

◆ handle_set_features()

| void handle_set_features | ( | NVME_ADMIN_COMMAND * | nvmeAdminCmd, |

| NVME_COMPLETION * | nvmeCPL | ||

| ) |

Definition at line 90 of file nvme_admin_cmd.c.

91{

92 ADMIN_SET_FEATURES_DW10 features;

93

95

97 {

99 {

100 nvmeCPL->dword[0] = 0x0;

102 break;

103 }

105 {

106 nvmeCPL->dword[0] = 0x0;

107 nvmeCPL->specific = 0x0;

108 break;

109 }

111 {

112 nvmeCPL->dword[0] = 0x0;

113 nvmeCPL->specific = 0x0;

114 break;

115 }

117 {

118 nvmeCPL->dword[0] = 0x0;

119 nvmeCPL->specific = 0x0;

120 break;

121 }

123 {

126 nvmeCPL->dword[0] = 0x0;

127 nvmeCPL->specific = 0x0;

128 break;

129 }

131 {

132 nvmeCPL->dword[0] = 0x0;

133 nvmeCPL->specific = 0x0;

134 break;

135 }

137 {

138 nvmeCPL->dword[0] = 0x0;

139 nvmeCPL->specific = 0x0;

140 break;

141 }

142 default:

143 {

145 ASSERT(0);

146 break;

147 }

148 }

150}

Definition: nvme.h:376

Here is the call graph for this function:

Here is the caller graph for this function:

Variable Documentation

◆ g_nvmeTask

|

extern |

Definition at line 71 of file nvme_main.c.