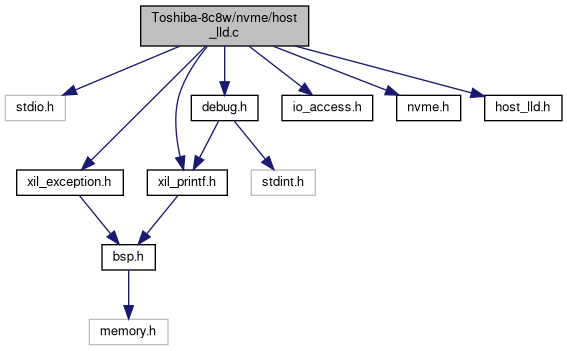

#include "stdio.h"#include "xil_exception.h"#include "xil_printf.h"#include "debug.h"#include "io_access.h"#include "nvme.h"#include "host_lld.h"

Go to the source code of this file.

Functions | |

| void | dev_irq_init () |

| void | dev_irq_handler () |

| unsigned int | check_nvme_cc_en () |

| void | pcie_async_reset (unsigned int rstCnt) |

| void | set_link_width (unsigned int linkNum) |

| void | set_nvme_csts_rdy (unsigned int rdy) |

| void | set_nvme_csts_shst (unsigned int shst) |

| void | set_nvme_admin_queue (unsigned int sqValid, unsigned int cqValid, unsigned int cqIrqEn) |

| unsigned int | get_nvme_cmd (unsigned short *qID, unsigned short *cmdSlotTag, unsigned int *cmdSeqNum, unsigned int *cmdDword) |

| void | set_auto_nvme_cpl (unsigned int cmdSlotTag, unsigned int specific, unsigned int statusFieldWord) |

| void | set_nvme_slot_release (unsigned int cmdSlotTag) |

| void | set_nvme_cpl (unsigned int sqId, unsigned int cid, unsigned int specific, unsigned int statusFieldWord) |

| void | set_io_sq (unsigned int ioSqIdx, unsigned int valid, unsigned int cqVector, unsigned int qSzie, unsigned int pcieBaseAddrL, unsigned int pcieBaseAddrH) |

| void | set_io_cq (unsigned int ioCqIdx, unsigned int valid, unsigned int irqEn, unsigned int irqVector, unsigned int qSzie, unsigned int pcieBaseAddrL, unsigned int pcieBaseAddrH) |

| void | set_direct_tx_dma (unsigned int devAddr, unsigned int pcieAddrH, unsigned int pcieAddrL, unsigned int len) |

| void | set_direct_rx_dma (unsigned int devAddr, unsigned int pcieAddrH, unsigned int pcieAddrL, unsigned int len) |

| void | set_auto_tx_dma (unsigned int cmdSlotTag, unsigned int cmd4KBOffset, unsigned int devAddr, unsigned int autoCompletion) |

| void | set_auto_rx_dma (unsigned int cmdSlotTag, unsigned int cmd4KBOffset, unsigned int devAddr, unsigned int autoCompletion) |

| void | check_direct_tx_dma_done () |

| void | check_direct_rx_dma_done () |

| void | check_auto_tx_dma_done () |

| void | check_auto_rx_dma_done () |

| unsigned int | check_auto_tx_dma_partial_done (unsigned int tailIndex, unsigned int tailAssistIndex) |

| unsigned int | check_auto_rx_dma_partial_done (unsigned int tailIndex, unsigned int tailAssistIndex) |

Variables | |

| NVME_CONTEXT | g_nvmeTask |

| HOST_DMA_STATUS | g_hostDmaStatus |

| HOST_DMA_ASSIST_STATUS | g_hostDmaAssistStatus |

Function Documentation

◆ check_auto_rx_dma_done()

| void check_auto_rx_dma_done | ( | ) |

Definition at line 477 of file host_lld.c.

◆ check_auto_rx_dma_partial_done()

| unsigned int check_auto_rx_dma_partial_done | ( | unsigned int | tailIndex, |

| unsigned int | tailAssistIndex | ||

| ) |

Definition at line 524 of file host_lld.c.

◆ check_auto_tx_dma_done()

| void check_auto_tx_dma_done | ( | ) |

Definition at line 469 of file host_lld.c.

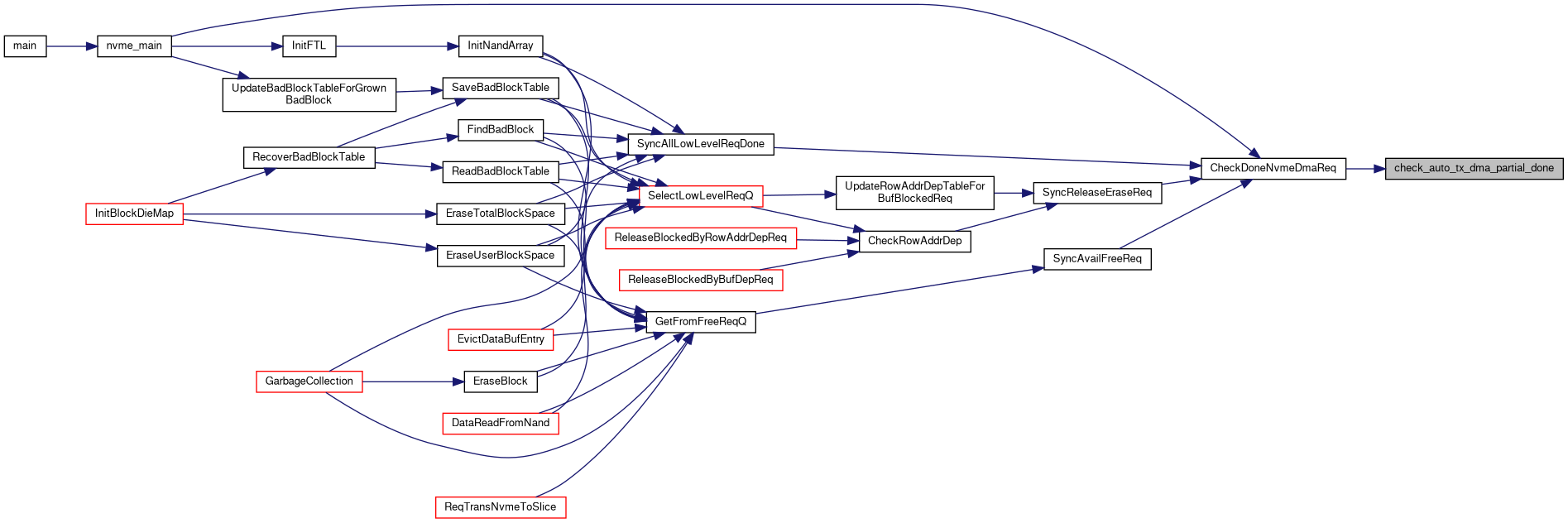

◆ check_auto_tx_dma_partial_done()

| unsigned int check_auto_tx_dma_partial_done | ( | unsigned int | tailIndex, |

| unsigned int | tailAssistIndex | ||

| ) |

Definition at line 485 of file host_lld.c.

◆ check_direct_rx_dma_done()

| void check_direct_rx_dma_done | ( | ) |

Definition at line 461 of file host_lld.c.

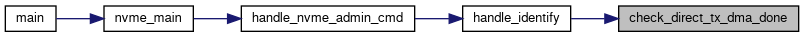

◆ check_direct_tx_dma_done()

| void check_direct_tx_dma_done | ( | ) |

Definition at line 453 of file host_lld.c.

◆ check_nvme_cc_en()

| unsigned int check_nvme_cc_en | ( | ) |

Definition at line 177 of file host_lld.c.

◆ dev_irq_handler()

| void dev_irq_handler | ( | ) |

Definition at line 86 of file host_lld.c.

◆ dev_irq_init()

| void dev_irq_init | ( | ) |

Definition at line 66 of file host_lld.c.

◆ get_nvme_cmd()

| unsigned int get_nvme_cmd | ( | unsigned short * | qID, |

| unsigned short * | cmdSlotTag, | ||

| unsigned int * | cmdSeqNum, | ||

| unsigned int * | cmdDword | ||

| ) |

Definition at line 237 of file host_lld.c.

◆ pcie_async_reset()

| void pcie_async_reset | ( | unsigned int | rstCnt | ) |

Definition at line 186 of file host_lld.c.

◆ set_auto_nvme_cpl()

| void set_auto_nvme_cpl | ( | unsigned int | cmdSlotTag, |

| unsigned int | specific, | ||

| unsigned int | statusFieldWord | ||

| ) |

Definition at line 260 of file host_lld.c.

◆ set_auto_rx_dma()

| void set_auto_rx_dma | ( | unsigned int | cmdSlotTag, |

| unsigned int | cmd4KBOffset, | ||

| unsigned int | devAddr, | ||

| unsigned int | autoCompletion | ||

| ) |

Definition at line 419 of file host_lld.c.

◆ set_auto_tx_dma()

| void set_auto_tx_dma | ( | unsigned int | cmdSlotTag, |

| unsigned int | cmd4KBOffset, | ||

| unsigned int | devAddr, | ||

| unsigned int | autoCompletion | ||

| ) |

Definition at line 385 of file host_lld.c.

◆ set_direct_rx_dma()

| void set_direct_rx_dma | ( | unsigned int | devAddr, |

| unsigned int | pcieAddrH, | ||

| unsigned int | pcieAddrL, | ||

| unsigned int | len | ||

| ) |

Definition at line 361 of file host_lld.c.

◆ set_direct_tx_dma()

| void set_direct_tx_dma | ( | unsigned int | devAddr, |

| unsigned int | pcieAddrH, | ||

| unsigned int | pcieAddrL, | ||

| unsigned int | len | ||

| ) |

Definition at line 336 of file host_lld.c.

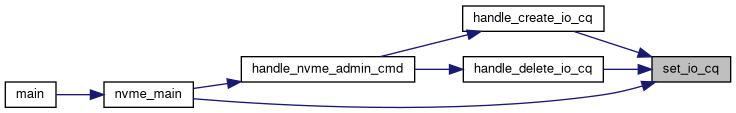

◆ set_io_cq()

| void set_io_cq | ( | unsigned int | ioCqIdx, |

| unsigned int | valid, | ||

| unsigned int | irqEn, | ||

| unsigned int | irqVector, | ||

| unsigned int | qSzie, | ||

| unsigned int | pcieBaseAddrL, | ||

| unsigned int | pcieBaseAddrH | ||

| ) |

Definition at line 318 of file host_lld.c.

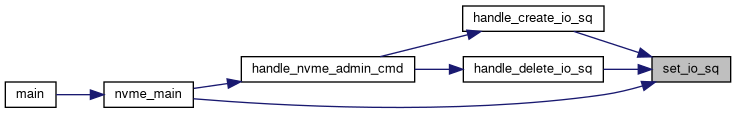

◆ set_io_sq()

| void set_io_sq | ( | unsigned int | ioSqIdx, |

| unsigned int | valid, | ||

| unsigned int | cqVector, | ||

| unsigned int | qSzie, | ||

| unsigned int | pcieBaseAddrL, | ||

| unsigned int | pcieBaseAddrH | ||

| ) |

Definition at line 301 of file host_lld.c.

◆ set_link_width()

| void set_link_width | ( | unsigned int | linkNum | ) |

Definition at line 195 of file host_lld.c.

◆ set_nvme_admin_queue()

| void set_nvme_admin_queue | ( | unsigned int | sqValid, |

| unsigned int | cqValid, | ||

| unsigned int | cqIrqEn | ||

| ) |

Definition at line 225 of file host_lld.c.

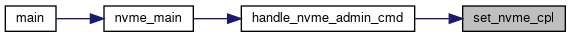

◆ set_nvme_cpl()

| void set_nvme_cpl | ( | unsigned int | sqId, |

| unsigned int | cid, | ||

| unsigned int | specific, | ||

| unsigned int | statusFieldWord | ||

| ) |

Definition at line 286 of file host_lld.c.

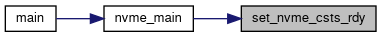

◆ set_nvme_csts_rdy()

| void set_nvme_csts_rdy | ( | unsigned int | rdy | ) |

Definition at line 205 of file host_lld.c.

◆ set_nvme_csts_shst()

| void set_nvme_csts_shst | ( | unsigned int | shst | ) |

Definition at line 215 of file host_lld.c.

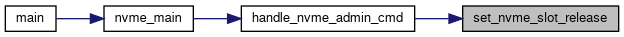

◆ set_nvme_slot_release()

| void set_nvme_slot_release | ( | unsigned int | cmdSlotTag | ) |

Definition at line 274 of file host_lld.c.

Variable Documentation

◆ g_hostDmaAssistStatus

| HOST_DMA_ASSIST_STATUS g_hostDmaAssistStatus |

Definition at line 64 of file host_lld.c.

◆ g_hostDmaStatus

| HOST_DMA_STATUS g_hostDmaStatus |

Definition at line 63 of file host_lld.c.

◆ g_nvmeTask

|

extern |

Definition at line 71 of file nvme_main.c.