#include "xil_cache.h"#include "xil_exception.h"#include "xil_mmu.h"#include "xparameters_ps.h"#include "xscugic_hw.h"#include "xscugic.h"#include "xil_printf.h"#include "debug.h"#include "nvme/nvme.h"#include "nvme/nvme_main.h"#include "nvme/host_lld.h"

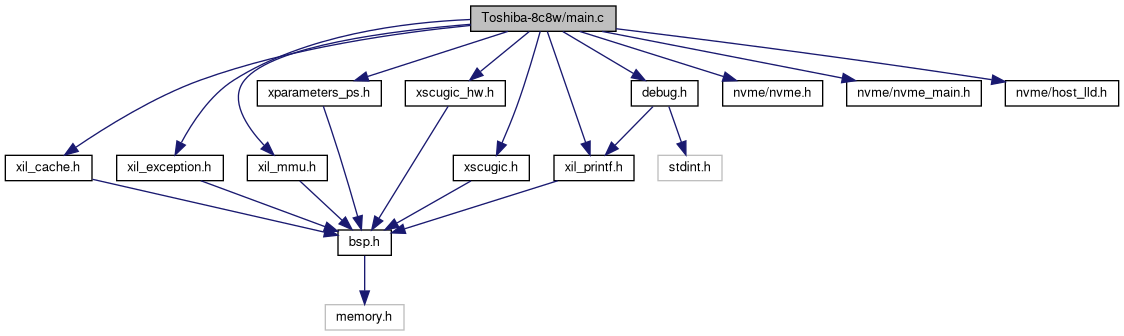

Include dependency graph for main.c:

Go to the source code of this file.

Macros | |

| #define | MB (1024 * 1024) |

Functions | |

| int | main () |

Variables | |

| XScuGic | GicInstance |

Macro Definition Documentation

◆ MB

| #define MB (1024 * 1024) |

Function Documentation

◆ main()

| int main | ( | ) |

Definition at line 76 of file main.c.

77{

78 unsigned int u;

79

80 XScuGic_Config *IntcConfig;

81

82 Xil_ICacheDisable();

83 Xil_DCacheDisable();

84 Xil_DisableMMU();

85

86// Paging table set

87#define MB (1024 * 1024)

88 for (u = 0; u < 4096; u++)

89 {

90 if (u < 0x2)

92 else if (u < 0x180)

94 else if (u < 0x400)

96 else

98 }

99

100 Xil_EnableMMU();

101 Xil_ICacheEnable();

102 Xil_DCacheEnable();

103 xil_printf("[!] MMU has been enabled.\r\n");

104

105 xil_printf("\r\n Hello COSMOS+ OpenSSD !!! \r\n");

106

107 Xil_ExceptionInit();

108

111 Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT, (Xil_ExceptionHandler)XScuGic_InterruptHandler,

112 &GicInstance);

113

115

117

118 // Enable interrupts in the Processor.

120 Xil_ExceptionEnable();

121

122 dev_irq_init();

123

124 nvme_main();

125

126 xil_printf("done\r\n");

127

128 return 0;

129}

#define MB

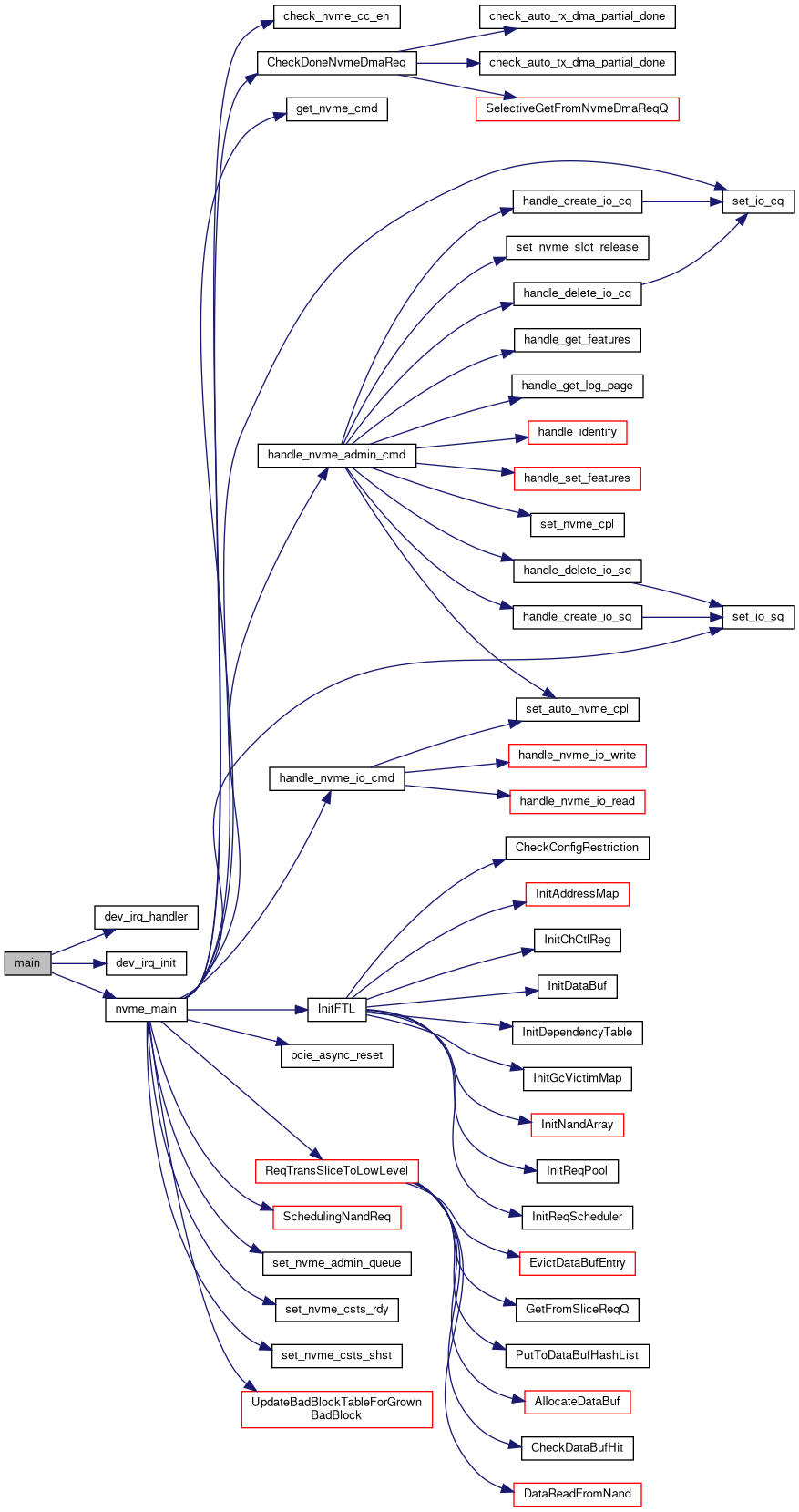

Here is the call graph for this function: